|

|

|

|

ТЕХНОЛОГИИ

|

Архитектура коммутаторов. Основные

принципы

Леонид Бараш

Сети передачи данных являются относительно молодой технологией,

однако они настолько естественно и прочно вошли в структуру

нашей цивилизации, что современный мир уже нельзя без них

представить. На глобальные сети опираются деятельность

банковских и биржевых систем, силовых структур, бизнес-операции

и управление компаниями и корпорациями, медицина и образование.

Они начинают конкурировать с существующими телекоммуникационными

сетями. Похоже, что общество стало заложником еще одной

технологии.

Без нарушения общности можно сказать, что инфраструктура

широкополосных коммуникаций базируется на взаимосвязанных сетях

разного масштаба. Однако какие бы протоколы верхнего уровня ни

реализовали эту взаимосвязь, то ли традиционные X.25 или Frame

Relay, то ли более современные ATM, ## на самом нижнем уровне мы

всегда найдем высокоскоростные коммутаторы, которые обеспечивают

передачу данных от отправителя к получателю.

Безусловно, особенности архитектуры коммутаторов во многом

определяются сетевой технологией. Тем не менее принципы

построения остаются общими. Поэтому для упрощения изложения

примем, что коммутатор содержит N входных и N выходных портов, а

поступающие пакеты имеют фиксированную длину (в терминологии ATM

такие пакеты называют ячейками).

Вообще говоря, коммутаторы выполняют довольно широкий набор

функций. Однако мы сосредоточим наше внимание на двух основных:

маршрутизация, или пересылка пакетов от входного порта на

выходной (адрес которого обычно указывается в заголовке пакета),

и разрешение конфликтов, возникающих в тех случаях, когда

несколько одновременно прибывших пакетов конкурируют за один и

тот же выходной порт. Последняя проблема решается обычно с

помощью той или иной схемы буферизации, которая зачастую и

определяет основные особенности архитектуры коммутатора.

Базовый коммутирующий элемент

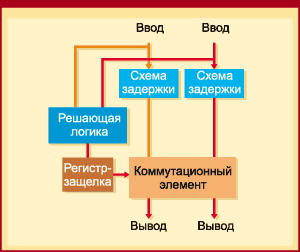

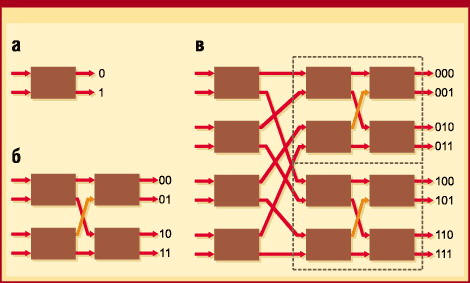

Начнем наше рассмотрение с так называемого бета-элемента (В-element),

реализующего функции коммутации для устройства с двумя входными

и двумя выходными портами (коммутатор 2 x 2). Во многих случаях

коммутаторы 2N x 2N строятся, как некая сетевая структура из

таких элементарных блоков. Они состоят из решающей логики,

которая обрабатывает заголовки пакетов, регистра-защелки,

фиксирующего результат решения, линии задержки, необходимой для

синхронизации операций, и непосредственно коммутационного поля (switch

fabric), выполняющего "прямое" или "кросс-соединение" входных и

выходных портов (рис. 1).

Рис. 1

Традиционные методы, используемые еще в телефонных сетях,

определялись как коммутация с пространственным разделением (Space-Division

Switching ## SDS), разделением по времени (Time-Division

Switching ## TDS) и их комбинацией. Метод пространственного

разделения происходит от технологии коммутации каналов. Он

заключается в том, что для соединения входного и выходного

портов создается физический канал. Обычно эта технология

реализуется с помощью коммутационной матрицы. Суть разделения по

времени упрощенно состоит в том, что каждый входящий пакет

занимает определенный временной слот, порядок которых

соответствует порядку выходных портов, и демультиплексор

"знает", в какой порт направить данный пакет. Однако современная

классификация архитектур коммутаторов основана на других

принципах. В соответствии с ними дизайн коммутаторов наиболее

часто описывается следующими четырьмя категориями:

-

с разделяемой памятью;

-

с разделяемой средой передачи;

-

с полносвязной топологией "каждый с каждым";

-

с пространственным разделением.

Теперь перейдем к более детальному анализу каждой из

перечисленных архитектур. В процессе изложения мы волей-неволей

вынуждены будем затрагивать вопросы буферизации, хотя более

полное рассмотрение связанных с этим проблем отложим на

дальнейшее.

Коммутаторы с разделяемой памятью

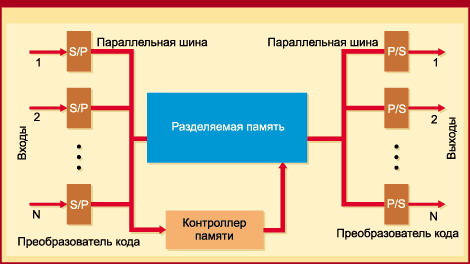

Основные принципы построения таких устройств иллюстрирует рис.

2. Трудность реализации этой архитектуры заключается в том, что

при наличии N входных (и выходных) портов быстродействие памяти

должно быть в N раз выше, чем скорость поступления данных в

порт. Поэтому такие коммутаторы оборудуются высокоскоростной

внутренней многоразрядной шиной, а поступающий поток бит из

последовательного кода преобразуется в параллельный. Для

обеспечения приемлемой частоты тактирования шину делают

достаточно широкой. Так, если W ## разрядность шины, то

необходимая тактовая частота будет в N/W раз меньше, чем

пропускная способность порта.

Рис. 2

Пакеты, предназначенные для разных портов, хранятся в специально

отведенных раздельных областях памяти. Будут ли эти разделы

фиксированной длины или переменной, зависит от особенностей

реализации обсуждаемой архитектуры. Очевидно, что разделы

переменной длины требуют более сложного управления, однако такой

подход позволяет в большинстве случаев решить проблемы

переполнения и значительно снизить потерю пакетов. Для

выполнения операций записи и чтения за один такт память делается

двухпортовой.

Поскольку увеличение количества портов требует соответствующего

повышения быстродействия памяти, то эта архитектура плохо

расширяется. Кроме этого, контроллер, осуществляющий управление

буферами, должен обрабатывать заголовки пакетов и маршрутные

теги с той же скоростью, с которой работает память. Поэтому

такой дизайн наиболее часто используется в небольших скоростных

коммутаторах для объединения локальных сетей. Однако даже для

коммутаторов средней (по количеству портов) величины требуемая

частота внутренней шины становится чрезмерно большой. Так, для

коммутатора с 32 входными портами и 16-разрядной шиной при

скорости поступления данных 155 Mbps на порт необходимая

тактовая частота внутренней шины составила бы 310 MHz.

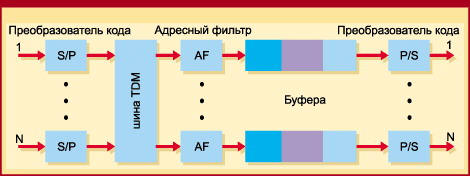

Коммутаторы с разделяемой средой передачи

Эта архитектура широко использовалась в ранних поколениях

многопортовых коммутаторов, предназначенных для сетей Ethernet

со скоростью передачи 10 Mbps. Пакеты поступали на шину

последовательно. Если применялось мультиплексирование с

разделением по времени (Time Division Multiplexing ## TDM), то

каждому временному слоту соответствовал определенный выходной

порт. Другое решение базировалось на адресных фильтрах, которые

направляли пакет к нужному порту на основе маршрутной

информации, содержащейся в заголовке пакета (рис. 3). Для

коммутации могла также использоваться адресная шина.

Рис. 3

Как и в предыдущем случае, основным ограничением для увеличения

количества портов или повышения скорости коммутации пакетов

служила частота, на которой могла оперировать шина. Чтобы не

допустить отбрасывания входных пакетов, скорость передачи должна

была быть не менее N x V, где N ## количество портов, а V ##

скорость входящего потока. На практике ее пропускная способность

обычно составляла около 2 Gbps.

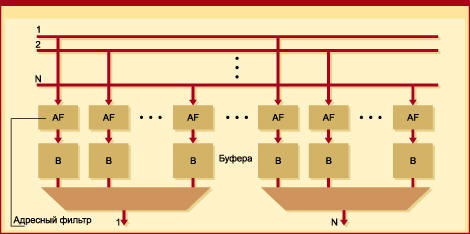

Коммутаторы с полносвязной топологией

При этом подходе между любой из N2 пар входных и выходных портов

существует независимый путь (рис. 4). Поступающие во входные

порты пакеты передаются по отдельным шинам ко всем выходным

портам, и там в работу включаются адресные фильтры. Такие

коммутаторы обычно оборудуются выходными буферами, количество

которых в классическом варианте равно N2.

Рис. 4

Полносвязный дизайн имеет ряд плюсов. В частности, легко

реализуются широковещательный и многоадресный режимы передачи.

Поскольку адресные фильтры и буфера должны работать со скоростью

поступления данных в порт, такая архитектура легко

масштабируется. Правда, за это нужно платить квадратичным ростом

числа выходных буферов. Поэтому компанией AT&T был предложен так

называемый коммутатор с выбыванием (knockout switch), с L

буферами для каждого выходного порта, т. е. их общее количество

составляло N x L. Это решение основывалось на предположении, что

одновременное поступление на вход более чем L пакетов является

маловероятным событием. Если же оно все же произойдет, то

дополнительный элемент, называемый концентратором, отберет

первые L, а остальные отбросит. Изменяя величину L, можно

регулировать долю потерянных пакетов. Отметим, что для

коммутаторов с выбыванием количество выходных буферов при

увеличении числа портов растет линейно, как N x L, а не

квадратично.

Коммутаторы с пространственным разделением

При пространственном разделении между парами входных и выходных

портов могут существовать как единственный, так и множественные

пути. Простейшим примером такой архитектуры является

коммутационная матрица (crossbar). В ней на каждом такте

синхронизирующего генератора контроллер анализирует адресную

информацию поступивших на входные порты пакетов и устанавливает

соединения между портами по выделенному каналу. Маршрутизация в

коммутационной матрице сходна с таковой в ячеистой сети.

Поскольку пропускная способность выделенного канала определяется

только физическими характеристиками передающей среды, то

суммарная скорость передачи данных в таких коммутаторах может

достигать более 100 Gbps. Однако в некоторых случаях при

неравномерно распределенном относительно портов трафике

производительность матричных коммутаторов может оказаться ниже,

чем устройств с разделяемой памятью. Стандартным методом решения

проблем, возникающих при конкуренции за выходной порт, является

использование той или иной схемы буферизации.

Для сокращения числа коммутационных элементов, необходимых при

внутренней коммутации каналов, были разработаны многокаскадные

сетевые архитектуры внутренних соединений (Multistage

Interconnection Networks ## MIN).

Прежде чем переходить к рассмотрению этого важного класса

коммутаторов, напомним некоторые определения. Говорят, что сеть

является самомаршрутизирующейся (self-routing), если состояние

каждого бета-элемента определяется только информацией,

содержащейся во входном пакете. Архитектура коммутатора

называется неблокирующей (non-blocking), если одновременно может

выполняться коммутация пакетов при любой перестановке путей от

различных входных к различным выходным портам. Показано, что

минимальное число бета-элементов, необходимое для

перестраиваемой неблокирующей сети, равно N log2 N. Такие сети,

также известные как сети Бенеша (Benes network), не являются

самомаршрутизирующимися. В этом случае для определения состояния

всех коммутационных элементов необходим контроллер.

Следовательно, для построения перестраиваемой неблокирующей

самомаршрутизирующейся коммутационной сети необходимо большее,

чем указано выше, число коммутационных элементов. Представленная

ниже архитектура является попыткой найти компромисс между

степенью использования соединений, долей потерянных пакетов и

сложностью дизайна.

В число наиболее распространенных многокаскадных архитектур

входят баньяноподобные коммутационные сети. Такое название они

получили потому, что их схема напоминает корни тропического

растения баньян (индийской смоковницы). Это

самомаршрутизирующаяся архитектура, которая, однако, использует

немного меньше бета-элементов, чем необходимо для построения

неблокирующего коммутатора. Более точно их число равно (N/2)

log2 N. Значит, можно получить такую комбинацию путей, что

пакеты не смогут коммутироваться одновременно. Поэтому для

обеспечения приемлемого количества потерянных пакетов необходима

какая-нибудь схема буферизации.

Баньяноподобные сети строятся с помощью взаимосвязанных каскадов

коммутационных элементов. Базовый коммутационный элемент 2 x 2

(рис. 5а) может маршрутизировать входящие пакеты, основываясь на

значении управляющего бита в поле адреса выходного порта: при

значении "0" пакет коммутируется "прямо", в противном случае ##

"наискосок". На рис. 5б представлена схема коммутатора 4 x 4,

состоящего из двух каскадов. Здесь для принятия решения о

маршруте необходимо использовать уже два адресных бита. При этом

первый бит может указывать номер коммутационного элемента, в то

время как второй ## адрес порта. Трехкаскадная сеть 8 x 8

формируется рекурсивно (рис. 5в). Для нахождения маршрута

используются три бита. По значению первого выполняется

коммутация в первом каскаде, после которого пакеты направляются

на "верхнюю" или "нижнюю" сеть 4 x 4, где повторяется описанный

ранее алгоритм.

Рис. 5

Коммутаторы на базе баньяноподобных сетей получили широкое

распространение благодаря использованию простых коммутационных

элементов. Кроме этого, поскольку обработка входящих пакетов

осуществляется параллельно и все элементы работают с одинаковой

скоростью, то отсутствуют дополнительные ограничения на число

входных портов и скорость поступающих пакетов при необходимости

расширения.

Как уже упоминалось выше, число элементов в коммутаторе N x N

типа баньяна меньше, чем необходимо для построения неблокирующей

архитектуры. Один из способов решения данной проблемы

заключается в упорядочении определенным образом поступающих на

входные порты пакетов. Такую процедуру выполняет, в частности,

сортировщик Бэтчера (Batcher), который устанавливается перед

коммутационной сетью. Однако если два пакета адресуются на один

выходной порт, то здесь от потери пакетов спасает только…

Буферизация

Какой бы архитектурный подход ни использовался при

проектировании коммутаторов, практически везде необходима

буферизация. Мы остановимся на трех базовых подходах, или схемах

размещения буферов.

Буферизация на входе. По этой схеме буфером оборудуется каждый

входной порт коммутатора. Чаще всего она используется в

неблокирующей архитектуре с пространственным разделением.

Входная буферизация помогает решить конфликт, при котором

несколько станций одновременно (в начале одного такта) пытаются

отослать пакеты на один и тот же выходной порт. Из буфера пакет

направляется в порт назначения только тогда, когда он становится

свободным. Схема эффективна для поддержки широковещательных и

многоадресных рассылок, однако страдает от так называемой

блокировки первым в очереди (head-of-queue blocking). Она

возникает в том случае, когда пакеты, стоящие в очереди, должны

быть направлены в различные порты. При этом если пакет В стоит

позади пакета А, чей порт занят, то он не будет отправлен даже

после освобождения своего порта. В некоторых коммутаторах

управляющая логика может просматривать адреса портов назначения

стоящих в очереди пакетов, и если порт для какого-либо из них

свободен, то он направляется вне очереди. Однако это значительно

повышает сложность коммутатора.

Буферизация на выходе. Этот тип буферизации предусматривает

организацию буферов при выходных портах. Обычно данная схема

применяется для коммутаторов с полносвязной топологией и с

разделяемой средой передачи. Для решения проблемы одновременной

доставки множества пакетов в один порт, как правило,

используется пул буферов, в идеале их количество для каждого

выходного порта должно совпадать с числом входных портов.

Отметим, что выходная буферизация не создает эффекта блокировки

первым в очереди.

Буферизация внутри коммутационного поля. В коммутаторах с

пространственным разделением буфера могут размещаться

непосредственно внутри коммутационных элементов. К примеру, в

баньяноподобных сетях базовые элементы могут содержать буфера

для каждого входного порта. Однако, кажется, такое решение имеет

больше недостатков, чем преимуществ. Во-первых, ему присуща

блокировка первым в очереди, особенно в случае небольших буферов

или многоэлементных сетей, а во-вторых, внутренние буфера вводят

непредсказуемую задержку при передаче пакетов по маршруту.

Суммарно это может значительно понизить производительность таких

устройств.

Как следует из вышесказанного, существует множество

разнообразных подходов при выборе архитектуры коммутаторов,

каждый из которых имеет свои преимущества и недостатки. Данная

публикация не претендует на роль пособия по выбору того или

иного решения, а лишь обрисовывает сложность задачи тонкой

настройки сети.

Компьютерное Обозрение #28, 19 - 25 июля 2000

|

|

|

КОНТАКТЫ |

г. Харьков

пер.Самеровский,1

Показать на карте

Т/ф:+38

(057) 7052094

Т:

+38 (057) 7191776

|

НАШИ ПАРТНЕРЫ |

|